[拼音]:butu sheji

[外文]:layout

根据微电子技术电路及其制造工艺的要求进行的掩模设计。布图设计一般包含布局(电路元件、器件的安置)和布线(电路元件、器件的互连)两个相互关连的设计步骤。布图设计的主要任务是按给定的制造工艺条件,完成电路元件、器件的布置和元件间必需的互连,保证:芯片有较高的布图密度;互连符合元件、器件的电学性能要求(如负载能力等);互连产生的寄生效应的影响(如连线寄生电容等)在设计要求允许范围以内并考虑设计制造周期、设计正确性验证和设计成本等。

布图设计方式除传统的人工设计外,主要的还有符号法设计方式、 栅阵列方式、 可编程序逻辑阵列方式、标准元或多元胞方式、母片或门阵列方式、任意元方式等。在大规模或超大规模集成电路设计中还经常采用分级设计的方法。

传统人工布图设计方式主要根据设计者的经验进行元件、器件的布置和互连设计。这种设计方式的灵活性大,布图密度高,但设计周期长、正确性验证困难,很难适应大规模和超大规模集成电路设计的需要。

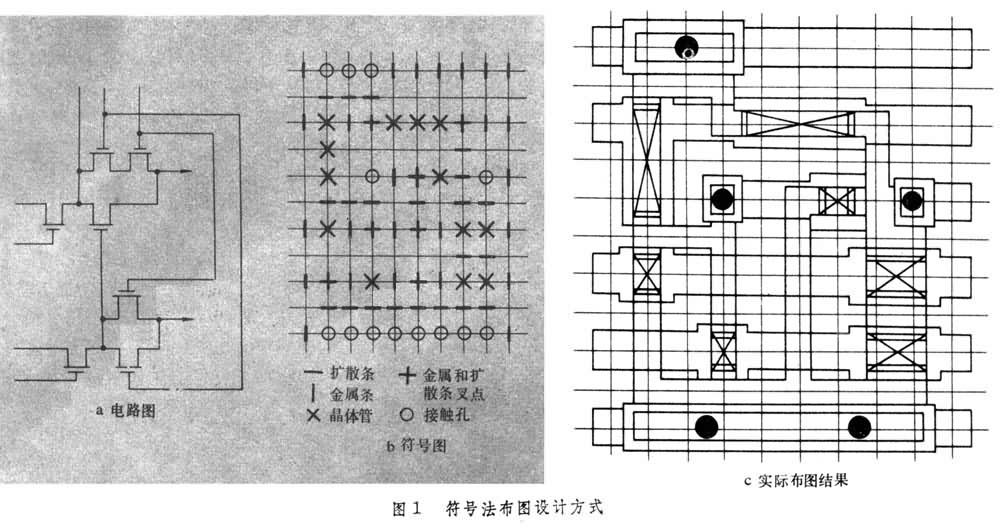

符号法布图设计方式首先根据电路和工艺条件。将电路的元件、连线、接触孔等规定为符号,并在由工艺条件确定的网格上用这些符号描述电路元件及其互连关系,然后由计算机软件自动产生实际的芯片布图。在设计中也可采用相对网格,用符号在网格上描述出电路的骨架图后,由计算机软件进行布图空间的压缩并产生实际芯片布图。这种设计方式可缩短作图和数字化的周期并可获得布图密度较高的设计结果(图1)。

栅阵列布图设计方式

栅阵列布图设计方式

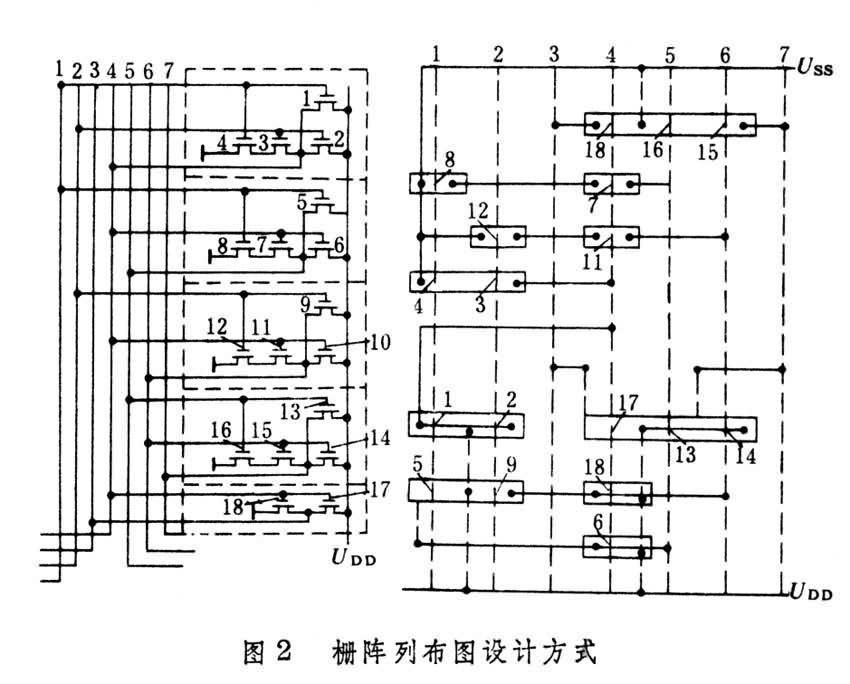

将 MOS电路的晶体管“嵌入“到互连线中,以提高芯片的布图密度。设计时把同时起连接和 MOS晶体管栅作用的多晶硅条(或铝线条)平行地排列成阵列的列(图2)。这些列一般对应于电路的输入、输出线。电路中相互并联或串联的晶体管的扩散区,通过扩散条或金属条连接起来构成阵列的行。在扩散区与多晶硅的交点处可形成电路的晶体管。电路所需的其他互连线,可用金属条或扩散条完成。

可编程序逻辑阵列布图设计方式

可编程序逻辑阵列布图设计方式

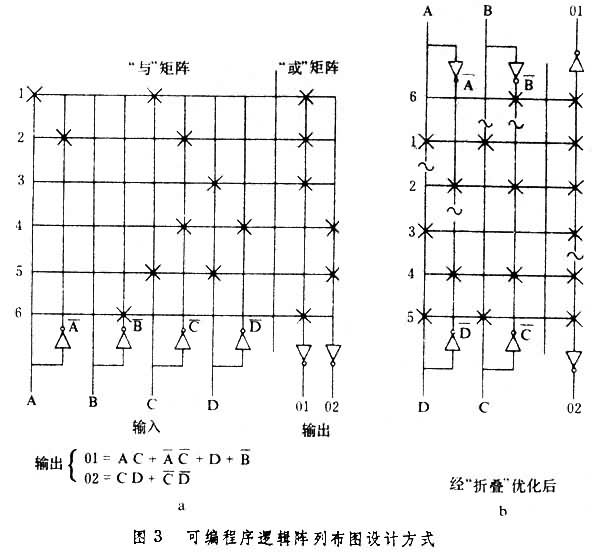

通常是面向随机组合逻辑电路。设计时,通过逻辑转换将电路等价地转换成一个规则的阵列式电路,使电路的输出成为输入的“与-或”函数。这样,电路就可用一个(或多个)“与”矩阵-“或”矩阵表示。电路的布图设计也就转化为规则的阵列式电路的设计(如只读存储器),见图3。在给出阵列的编码表以后,布图可由计算机自动地完成。由于转换得到的阵列一般是相当稀疏的,芯片布图密度就比较低,往往需要对设计结果进行分段“折叠”优化,压缩冗余的布图面积,以提高布图密度。

标准单元布图设计方式

标准单元布图设计方式

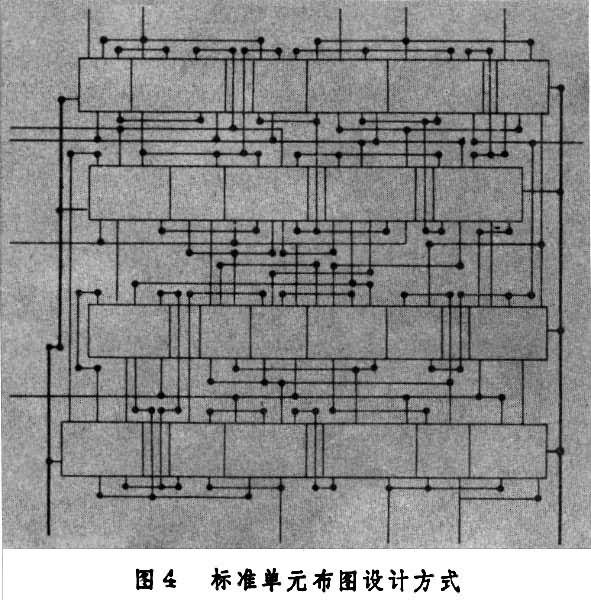

利用预先设计好的标准单元进行电路布图设计。标准单元在电学上可以是一个逻辑门或触发器等功能子电路。这些单元的高度相同,长度不同。所有的输入、输出接点排列在单元的上、下一边或两边上。地线和电源线排列在单元的左右两边(图4)。布图设计时,计算机根据电路的互连关系将单元成行地排列,行内单元的地线、电源线同时实现了互连,电路单元的其他互连在单元行间和两端的布线通道区中间完成,一般采用双层布线,可由计算机软件自动完成。单元行间的距离可根据布线的实际需要进行调整。这是一种自动化设计方式,设计周期短,但布图密度低于人工设计方式。

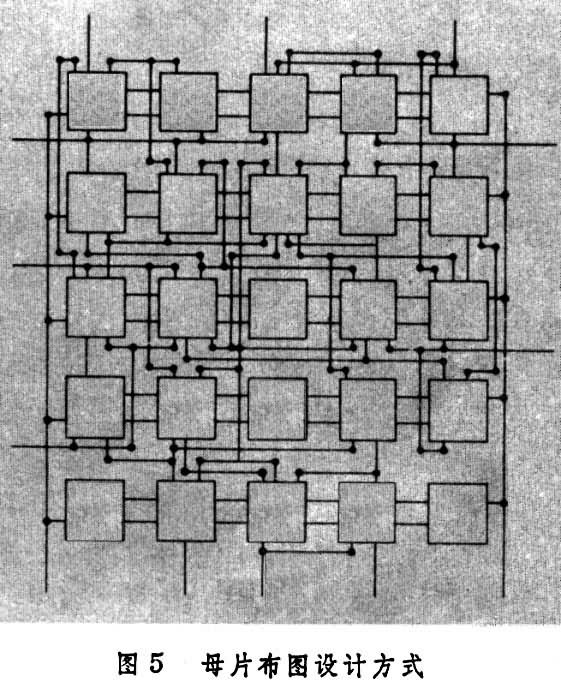

母片布图设计

母片布图设计

利用预先制造好的“母片”进行电路布图设计(图5)。通常母片上以阵列形式排列着大小、形状相同的待互连的基本单元(一般为逻辑门)。设计时,首先根据电路的互连要求进行单元分配,使电路的单元与母片上一个或若干个固定的基本单元建立对应关系。然后,在基本单元间的布线区内实现单元间所需的互连,其主要设计过程可由计算机自动完成,设计周期短。除布线有关的工艺步骤外,其他工艺步骤(母片的制备)都可在具体的电路布图设计前成批地完成。因此,在布图设计完成后设计者可很快地得到所需的芯片。由于利用预先制备的母片,通常在芯片上有较多的冗余单元,布图密度较低;对于复杂的电路,不能保证自动地完成全部所需的互连,往往需要对少数剩线再进行人工设计。

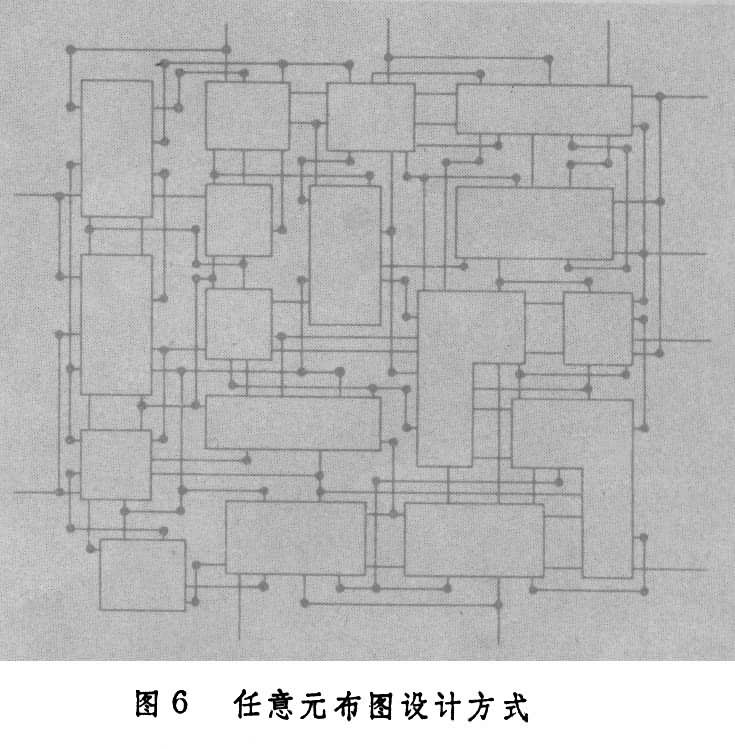

任意元布图设计方式

任意元布图设计方式

利用预先设计好的功能单元电路进行布图设计(图6)。单元的形状和大小可以是任意的(一般为矩形)。互连接点排列在单元的边界上。布图设计时,根据互连要求和单元的形状、大小进行单元的布置。然后,在功能单元间的布线区中实现单元间的互连。设计结果具有较高的布图密度。

分级布图设计方式

分级布图设计方式

可分为自顶向下和自底向上两个设计过程。在自顶向下设计过程中,先把电路划分为若干个大小不同、互连关系比较松散的子电路,并根据各子电路和总的设计要求概略地确定出各子电路的布图设计结果的形状、大小和位置。然后,分别根据各子电路的性质选用适当的设计方式进行布图设计,并尽可能使设计结果满足上一级设计提出的形状、大小和引出接点位置等要求。在子电路的布图设计中还可以继续分级,最后完成各子电路的互连而获得所需芯片的布图设计。

在自底向上设计过程中,首先根据子电路自身的要求进行最低一级子电路的设计。然后,根据设计结果的形状、大小和相互间的连接关系,决定其各自的位置,实现互连而形成上一级的子电路布图结果。继续上述过程,直至完成整个电路的布图设计。