[拼音]:weidianzi zuzhuang

[外文]:microelectronic packaging

根据电原理图或逻辑图,运用微电子技术和高密度组装技术,将微电子器件和微小型元件组装成适用的、可生产的电子硬件的技术过程。

微电子组装是新一代电子组装技术。它是一门新型的电路、工艺、结构、元件、器件紧密结合的综合性技术,涉及到集成电路固态技术、厚膜技术、薄膜技术、电路技术、互连技术、微电子焊接技术、高密度组装技术、散热技术、计算机辅助设计、计算机辅助生产、计算机辅助测试技术和可靠性技术等领域。

微电子组装一方面尽可能减小芯片和元件、器件的安装面积、互连线尺寸和长度,以提高组装密度和互连密度;另一方面则尽可能扩大基板尺寸和布线层数,以容纳尽可能多的电路器件,完成更多、更重要的功能,从而减少组装层次和外连接点数。

微电子组装与常规的电子组装的主要区别在于所用的元件、器件、组装结构和互连手段不同。前者以芯片(载体、载带、小型封装器件等)多层细线基板(陶瓷基板、表面安装的细线印制线路板、被釉钢基板等)为基础;后者以常规的元件、器件-印制线路板为基础。微电子组装的组装密度可比常规电子组装高5倍以上,互连密度高6~25倍,乃至100倍(薄膜布线技术),因此能减小电子设备的体积、减轻重量、加快运算速度(信号传输延迟时间减小)、提高可靠性、减少组装级。

微电子组装技术的发展始于20世纪40年代末和50年代初的微模组件和后来发展的薄膜和厚膜混合电路及微波集成电路。70年代以来,微电子组装技术发展更快,又出现了芯片载体、载带、大面积多芯片多层厚膜电路。

70年代末至80年代初,门阵列芯片、密封载体-陶瓷基板、被釉钢基板和表面安装印制线路板组件得到广泛应用,多层薄膜混合电路和有机聚合物厚膜电路也在迅速发展。

高集成度的芯片

采用集成度高的芯片,如集成电路芯片、晶体管芯片、电阻芯片、电容芯片以及其他微型元件、器件(如小型封装集成电路、晶体管),以取代常规的元件、器件等。改进芯片安装方法是缩小体积、提高组装互连密度、提高可靠性的一项重要技术。

(1)倒装片法和线焊法:属直接安装法,安装面积小,但芯片不能预测(老化筛选),影响混合电路或微电子组装组件的合格率和可靠性。

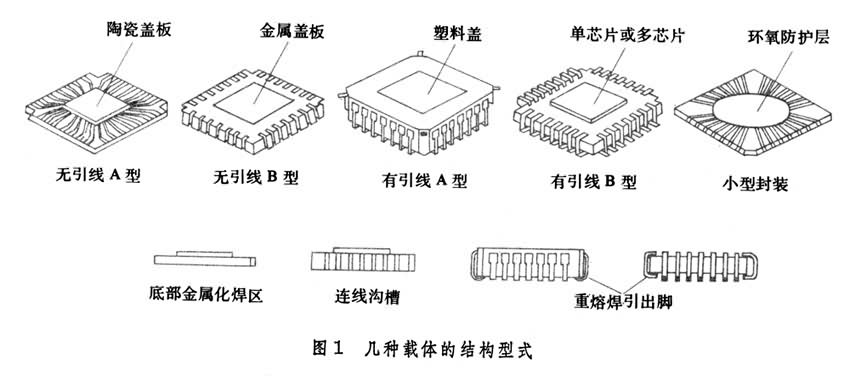

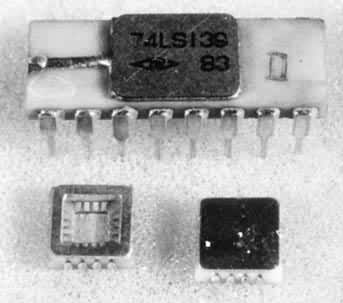

(2)芯片载体法:这是一种可预测的微小型芯片封装型式,四边和底部都引出焊区(或引线),最多达300多个。载体有多种结构型式(图1)。带有塔状散热器的有引线密封的载体和 4芯片的载体。密封陶瓷载体的可靠性高,应用广,其面积约为双列直插式外壳的1/4~1/20(图2)。

(3)载带法:一种供芯片安装、互连、预测的特殊软性印制线路,外形像电影胶卷。其特点是自动化生产程度高。现代采用的技术有载带自动焊接技术和凸点载带自动焊接技术。

微小型高密度互连和组装技术

包括厚膜混合电路、薄膜混合电路、微波集成电路。

(1)密封载体-多层细线基板组件是采用高密度互连和组装技术的一种组件。这种组件的优点是:可使用各种基板(如陶瓷基板、被釉钢基板、印制线路板和酚醛纸板等);敏感的芯片可封装在密封载体中,组件不需要大封装外壳,体积重量远小于混合电路;工艺性、可调试性、可维修性好;散热性好;用气相重熔焊技术可以在基板两面都安装载体,提高组装密度。

(2)多层陶瓷基板是现代用得最多的一种基板,丝网印刷厚膜导体线宽一般为0.1~0.2毫米,布线网格间距 0.25~0.5毫米。其制造方法有干法和湿法两种。干法布线层数一般不超过10层,湿法布线层数可做到33层,但其制造工艺比干法复杂。在一块基板上可组装多达一百多个芯片(载体、载带),其功能相当于常规电子组装的一个分机、分系统乃至整机。这样,组装层次和外互连接点数就大为减少。数字电路或模拟电路的印制电路板部件可用芯片(载体、载带)-基板组件实现微电子组装,其体积、重量可缩小为原来的五分之一至几十分之一。

细线印制板表面安装技术也是一种新的微电子组装方法。

(3)有机聚合物厚膜电路是在酚醛纸板、环氧玻璃纤维布板等基板上印刷的有机聚合物厚膜电路。它可与芯片、载体、载带组装和焊接,其特点是固化温度低、价廉。

(4)有机薄膜多层薄膜电路的互连布线密度比厚膜电路的高,布线网格可达0.1毫米,甚至更小。

(5)微波组件包括单芯片微波集成电路和微波功放组件。前者是将微波晶体管和微波集成电路做在一片很小的砷化镓基片上;后者是将微波晶体管-载体组装在氧化铝基板微波集成电路上。L波段输出功率100瓦,可使发射机固态化、小型化,已用于相控阵雷达。

IBM3081处理机热传导组件是一种新型的微电子组件。它采用湿法28~33层布线,在90×90毫米陶瓷基板上安装 118个大规模集成高速双极型逻辑电路芯片和门阵列芯片。每个芯片有120多个焊区,按0.25×0.25毫米网格矩阵排列。组件共含35万个通孔,厚膜导体最细0.08毫米,其生产、检测、调试过程全由计算机控制。输入和输出为1800个针阵列引线,通过零插拔力插座与大型20层细线印制板(600×700毫米)互连。由于功耗达300瓦,采取活塞顶住芯片导热、水冷、充氦等散热措施,使所有芯片的结温保持在40~85 。后来日本和美国又研制成功微间隙导热、风冷散热组件,使组件结构更为简单、轻巧。

。后来日本和美国又研制成功微间隙导热、风冷散热组件,使组件结构更为简单、轻巧。

更高组装级的微电子组装技术

70年代末到80年代初,机载、弹载、舰载电子设备采用密度更高的微电子组装产品。例如,有一种机载计算机由 8块108×150毫米的密封载体-多层陶瓷基板构成,体积仅有30×160×230毫米。IBM公司的4381计算机采用22个微间隙导热风冷组件(每个组件尺寸为64×64毫米,含31~36个大规模集成芯片)装在一块600×700毫米22层细线印制板上。只用一块印制电路板完成常规电子组装的一个机柜才能完成的中央处理器功能。日本电气公司的SX-2超级计算机采用先进的高速大规模集成芯片和高速高密度微电子组装技术实现了6纳秒机器周期,每秒 13亿次浮点运算速度。

散热冷却技术

微电子组装的关键技术之一。由于体积小、电路密度高和功率密度大,新型单芯片功率最大达12瓦,组件功率密度达4瓦/厘米2。因此,必须采用高效的冷却方法。除一般加散热器风冷外,还有冷板、液冷、热管、沸腾冷却等方式(见电子设备热控制)。

微小型连接器

它尺寸小,插脚多,接触可靠,具有零插拔力或低插拔力。

微电子组装设计

在设计中必须考虑电路划分、组装结构、布线设计、信号传输延迟、分布参数的影响、阻抗匹配、串扰抑制、电源、地系统的压降、共耦、去耦、屏蔽、散热等问题。

微电子组装工艺

主要包括精细基板制造、芯片安装、焊接、老化测试、密封、电路调试等工艺技术。

用大规模、超大规模、超高速集成电路需要结合先进的组装技术,方能做出先进的电子设备。现代电子设备,对微电子组装的要求越来越高。正在研究中的新的微电子组装技术,还有多基板高密度叠装组件、新的多层细线基板技术、散热技术、不需焊接的微互连技术以及声、光、电结合的微电子组装技术等。

- 参考书目

- Jerry Lyman, Microelectronic Interconnection and Packaging,McGraw-Hill,New York,1980.

- C.A.Harper,Handbook of Electronic Packaging,McGraw-Hill,New York,1969.